(3 Hours) Max. marks: 80

- **N.B.:** (1) Question No. 1 is compulsory.

- (2) Solve any three questions from the remaining five questions.

- (3) Figures to the right indicate full marks.

- (4) Assume suitable data if necessary and mention the same in answer sheet.

- Q.1 Attempt **any 4** questions

[20]

- (a) List the steps involved in fabrication process of MOSFET.

- (b) Compare the output resistance of the cascade MOSFET current source to that of the two-transistor current source. Assume  $I_{REF} = I_O = 100 \,\mu\text{A}$  in both the circuits,  $\lambda = 0.01 \,\text{V}^{-1}$  for all transistors, and  $g_m = 0.5 \,\text{mA/V}$ .

- (c) Draw a mask layout of NMOS transistor.

- (d) Derive the equation for output resistance of common gate amplifier.

- (e) Draw the equivalent model for transformer and explain.

- (f) List the second order effects in MOSFET. Discuss any one of them.

- Q.2 (a) Why is scaling required? Discuss the various types of scaling. [10]

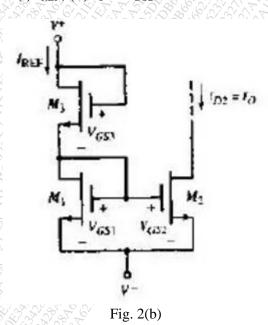

- (b) Consider the MOSFET current source in Fig. 2 (b) with  $V^+ = 10$  V and  $V^- = 0$ , and [10] the transistor parameters are:  $V_{TN} = 1.8$  V,  $\frac{1}{2} \mu_n C_{ox} = 20 \mu \text{A/V}^2$ , and  $\lambda = 0.01$  V<sup>-1</sup>. The transistor width-to-length ratios are:  $(W/L)_2 = 6$ ,  $(W/L)_1 = 12$ ,  $(W/L)_3 = 3$ . Determine (i)  $I_{REF}$ , (ii)  $I_O$  at  $V_{DS2} = 2$  V.

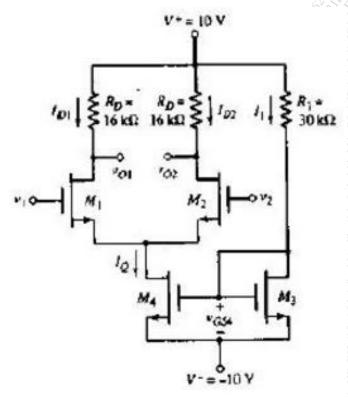

Q.3 (a) Consider the differential amplifier shown in Fig. 3(a). The transistor parameters are:  $K_{n1}=K_{n2}=0.1$  mA/V<sup>2</sup>,  $K_{n3}=K_{n4}=0.3$  mA/V<sup>2</sup>, and for all transitors,  $\lambda=0$  and  $V_{TN}=1$  V. Determine the maximum range of common-mode input voltage.

P.T.O

53615 Page 1 of 3

Fig. 3(a)

- (b) With a neat circuit explain Bias Independent Current Source using MOSFET. [10]

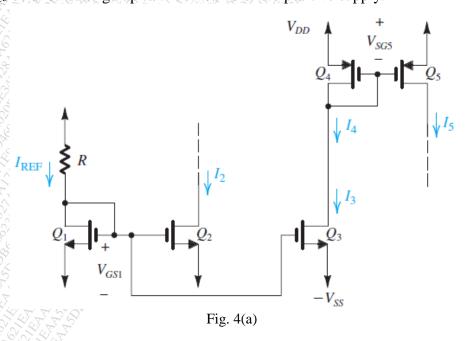

- Q.4 (a) For the circuit shown in Fig. 4(a), let  $V_{DD} = V_{SS} = 1.5 \text{ V}$ ,  $V_{TN} = 0.6 \text{ V}$ ,  $V_{TP} = 0.6 \text{ V}$ , all channel lengths = 1  $\mu$ m,  $k_n$ '=200  $\mu$ A/V<sup>2</sup>,  $k_p$ '=80  $\mu$ A/V<sup>2</sup>, and  $\lambda$ =0. For  $I_{REF} = 10 \mu$ A, find the widths of all transistors to obtain  $I_2 = 60 \mu$ A,  $I_3 = 20 \mu$ A, and  $I_5 = 80 \mu$ A. It is further required that the voltage at the drain of  $Q_2$  be allowed to go down to within 0.2 V of the negative supply and that the voltage at the drain of  $Q_5$  be allowed to go up to within 0.2 V of the positive supply.

P.T.O

53615 Page 2 of 3

## Paper / Subject Code: 32205 / Elective - I Microlectronics (DLOC)

| (b) | Draw a small signal equivalent structure of Diff-amp and derive the equation for its CMRR. | [10] |

|-----|--------------------------------------------------------------------------------------------|------|

| (a) | Draw a neat diagram of Class B power amplifier. Derive equation for its efficiency.        | [10] |

| (b) |                                                                                            | [10] |

Q.6 Short notes on: (Attempt any four)

[20]

- (a) Short channel effects in MOSFET.

- (b) Wilson Current Mirror.

Q.5

- (c) MOS device capacitances.

- (d) Folded cascode MOS amplifier.

- (e) Fabrication of inductors.

\*\*\*\*\*\*

53615 Page 3 of 3