## Paper / Subject Code: 51202 / Electronics Devices and Circuits-I

QP: Code: 25071

(3 Hours)

[Total Marks: 80

Note: 1) Question no. 1 is compulsory.

- 2) Solve any three questions out of remaining.

- 3) Fig. to the right indicates maximum marks.

- 4) Assume suitable data wherever necessary but justify the same.

## Q1. Solve any five.

(5x4 = 20)

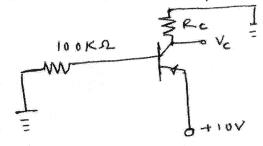

a) Determine the value of Rc such that Vc = 5V and  $\beta = 50$ .

- b) State and explain Miller's Theorem.

- c) Design a self bias circuit using JFET for  $I_D$  = 3mA,  $V_{DD}$  = 20 V and  $V_{DS}$  = 0.6  $V_{DD}$ . (  $I_{DSS}$  = 8 mA,  $V_P$  = -4V )

- d) Explain various types of capacitors.

- e) Determine the values of coupling capacitors  $C_{C1}$  and  $C_{C2}$  if  $r_{\Pi}$  = 1.5K $\Omega$ ,  $\beta$  = 120 and  $f_L$ =20Hz.

f) Explain concept of zero temperature drift in JFET.

**TURN OVER**

QP Code: 25071

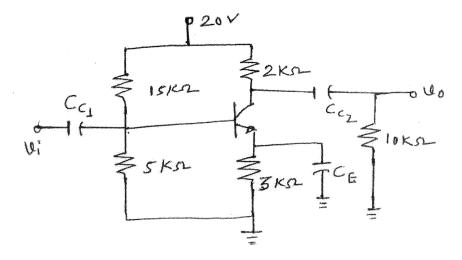

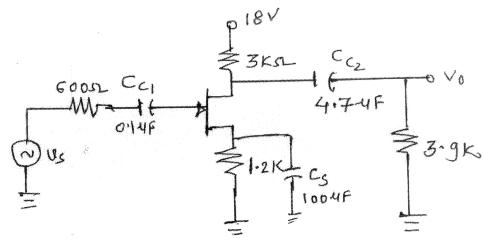

Q2. A) Calculate 1) IBO, ICO

2) g<sub>m</sub>, r<sub>∏</sub>

3) Small signal voltage gain

10

2

Q2 B) Explain the concept of LC filter in power supply circuit and hence derive

10

expression for ripple factor of LC filter.

Q3 A) Explain concept of shunt Zener regulator. For a shunt Zener regulator giving

10

output voltage of 10 V and load resistance varying from  $5K\Omega$  to  $10K\Omega$ , Vin is varying between 18V to 22V.

Find Rs, Pzmax, Sv and Ro.

Assume  $Rz = 4\Omega$  and  $Izmin = 50\mu A$ .

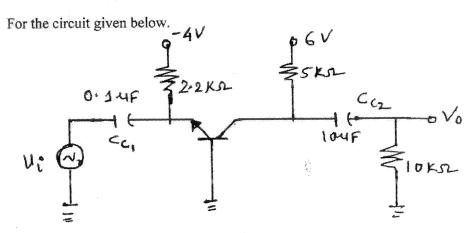

B) Determine  $I_{DQ}$ ,  $V_{GSQ}$ ,  $V_{DSQ}$  if  $I_{DSS} = 9mA$  and  $V_P = -3V$  for the circuit given below.

10

Q4 A) Design capacitive filter with FWR using two diodes with ripple factor less than 5%.

10

Output voltage is 24V and load current 200mA. The input line voltage of 230V/50Hz Is available.

B) Determine the values of biasing components for a CE configuration if Vcc = 12V,

10

$V_{CE} = 6V$ , Re=1K $\Omega$ ,  $V_{BE} = 0.6V$ ,  $\beta = 180$  for the following circuit.

- i) Fixed bias without R<sub>E</sub>

- ii) Voltage Divider bias with  $V_{RE} = 10\%$  of Vcc and  $S_1 = 8$

TURN OVER

**QP Code: 25071**

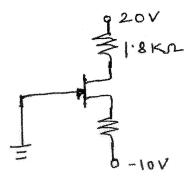

Q5 A) For JFET if

$$I_{DSS} = 6$$

mA,  $V_P = -6V$  rd = $\infty$ , Cgd = 4pF, Cgs = 6pF, Cds = 1pF 15

Determine i) V<sub>GSQ</sub> ii) I<sub>DQ</sub>

- iii)gmo

- iv) gm

- v) Midband voltage gain Av

- vi) Higher cut off frequency

B) Explain high frequency ∏ equivalent model of common emitter BJT.

5

Q6. Design single stage CS amplifier using mid-point biasing method for voltage gain of 12, 20

$$F_L = 20 \text{ Hz}, R_L = 10 \text{K}\Omega, V_0 = 3.5 \text{V}$$

(Use JFET parameters  $I_{DSS}$  = 7mA,  $V_P$  = -2.5V, gmo =  $5600\mu \mho, \, rd$  =  $50 K\Omega$  )