(3 Hours)

Total Marks: 80

- 1. Question No.1 is compulsory.

- 2. Answer any three from remaining questions.

- 3. Figures to the right indicate full marks.

- 4. Assume suitable data if required.

## Q1. Attempt any four.

- a Explain the effect of temperature of on VI characteristics of a PN junction diode. 05

- b What are the important parameters of a JFET? How these parameters are determined graphically?

- c What is Early effect? Explain how it affects the BJT characteristics in CB configuration.

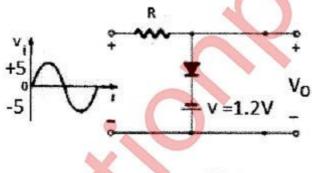

- d For the circuit shown in figure.1 draw the output waveform. Assume diode is ideal.

Fig.1

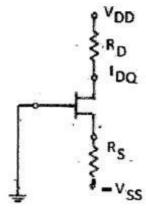

e For the FET shown in figure.2 the drain current equation is

$$I_{DQ} = 9 \left(1 + \frac{V_{GSQ}}{3}\right)^2$$

mA, Determine  $I_{DQ}$ ,  $V_{GSQ}$ ,  $V_{DSQ}$ ,  $V_D$

$V_{DD}=20V$ ,  $R_{D}=2k\Omega$ ,  $R_{S}=1.5k\Omega$ ,  $-V_{SS}=-10V$ .

Fig.2

05

- Q2. Describe the construction and operation of an N-channel MOSFET in enhancement mode. Draw its characteristics and equivalent circuit of the device.

- 10

- Describe the different MOSFET biasing techniques . Determine the drain current, 10 drain to source voltage, and Power dissipated in the transistor of CS circuit with an N-channel E MOSFET shown in figure 3.  $R_1 = 30k\Omega$ ,  $R_2 = 20k\Omega$ ,  $R_D = 20k\Omega$  $20k\Omega$ ,  $R_S = 0.5k\Omega$ ,  $V_{DD} = 5V$ ,  $V_{TN} = 1V$ ,  $k_N = 0.1mA/V2$

Fig.3

- Q3. Draw input and output characteristics of CE amplifier. Explain graphical analysis to determine parameters.(Zi, Zo, AV, and Ai)

- 10 In the Common Emitter configuration with voltage divider bias  $I_E = 1mA$  $V_{CE}=2V$  ,  $R_E=1k\Omega$  and eta=49 . Determine the values of  $R_C$  ,  $R_1$  and  $R_2$  such that the stability factor does not exceed 5. Assume  $V_{\rm CC}=5V$  and  $V_{\rm BE}=0.3V$  .

- For the amplifier shown in figure.4 analyze and determine Q4.

10

- i) Small-signal hybrid pi parameters of BJT

- ii) Small-signal voltage gain

- Input and output impedance.

The circuit parameters are:  $R_1=56k\,\Omega$  ,  $R_2=12.2k\,\Omega$ ,  $R_E=0.4k\,\Omega$ ,  $R_C = 2k\Omega$ ,  $R_L = 10k\Omega$ ,  $V_{CC} = 10V$  and BJT parameters are  $\beta = 100, V_{BE} = 0.7V$

Fig.4

- b Draw JFET CS amplifier with voltage divider bias and derive the expressions for the voltage gain, input impedance and output impedance.

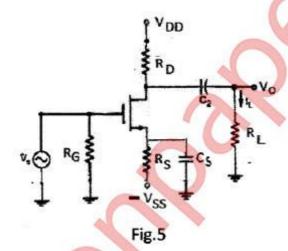

- Q5 a For the amplifier shown in figure.5 derive the expression for voltage gain, input 10 and output impedance. The parameters of the MOSFET in the circuit shown in fig .5 are;  $R_G = 1M\Omega$ ,  $V_{DD} = 5V$ ,  $-V_{SS} = -5V$ ,  $V_{TN} = 0.8 V$ ,  $k_N = 0.85 mA/V^2$

- (i) Determine the values of  $R_S$  and  $R_D$  such that  $I_{DQ}$ =0.1mA and maximum symmetrical 1V peak sinusoidal signal occurs at output.(ii) Find the small signal transistor parameters. (iv) Determine the small-signal voltage gain  $A_V$

- b Draw the circuit diagram of Wein Bridge Oscillator and derive the expression for the frequency of oscillation and minimum gain required for sustained oscillation

- Q6 Write a short note on following 20

- a Twin-T Oscillator.

- b Varactor Diode (Construction and operation)

- c D C load line concept in BJT. Why Q point should be at the middle of DC load line and fixed?

- d MOS capacitor

\*\*\*\*\*\*\*\*